SD cards are used in thousands of products, including digital cameras, smartphones & tablets, and other portable devices.

SD/SDIO Host Controller IP Core allows an embedded system to access an SD card or SDIO device via I/O pins of the FPGA and enables easy integration with the rest of the system. It acts as a mediator between a processor and an SD card enabling the command and data communication between the SD driver and SD card.

The iWave SD/SDIO Host Controller IP is fully compliant with SD Host Controller Specification Version 3.0 and Physical Layer Specification Version 3.0. It enables the host to access SD memory cards or SDIO devices. The IP has native support for all SD/SDIO commands and supports SD, MicroSD, SDHC, SDXC, and SDIO cards.

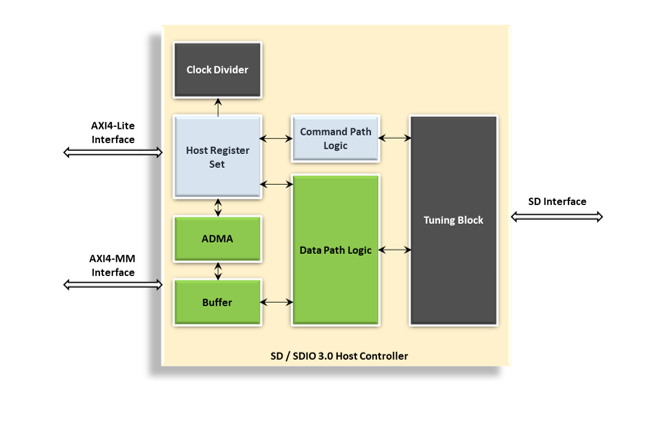

Following is the block diagram of SD/SDIO Host Controller 3.0 IP, which consists of the following main blocks:

- Command Path Logic to implement the logic required for sending commands to the SD card and receiving the response from the SD card.

- Data Path Logic manages the process of writing and reading the data between the host and the SD card. The buffer block can handle up to 2KB of FIFO on each read and write direction.

- The standard SD Host Register Set stores all the SD host controller configuration and status information of the SD host controller. Several registers are implemented as per the SD host specification, including the Response register, Command Generation register, Buffer Port, Configuration, and interrupt Control register.

- The ADMA module manages the data transfer to and from the host memory during write and read operations.

- Tuning block implements the tuning logic as per the SD specification using the FPGA device specific IO primitives.

The SD Host Controller IP supports default speed, high-speed and operations up to 104Mbps and 1-bit and 4-bit SD transactions. The built-in 2KB data buffer enables efficient communication with the host processor at low interrupt latency.

Key features of the SD/SDIO Host Controller are:

- Support Default speed and High-Speed including SDR12, SDR25, DDR50, SDR50 andSDR104 modes

- Includes ADMA2 (scatter-gather) engine

- Programmable 1-bit, 4-bit bus width

- Supports both single block and multi-block data transfer

- Supports 32-bit AXI4 memory mapped interface towards host processor

- Supports 32-bit AXI4 lite interface toward SD Host Controller

- Cyclic Redundancy Check (CRC) for command and data

- Supports timeout monitoring for the response, data, CRC token & busy

- Support for the following UHS –I modes of operations ensure compatibility with any card available in the market.

- SDR12 – SDR up to 25MHz 1.8V signalling

- SDR25 – SDR up to 50MHz 1.8V signalling

- SDR50 – SDR up to 100MHz 1.8V signalling

- SDR104 – SDR up to 208MHz 1.8V signalling

Benefits

- The IP architecture leverages power management techniques, making it ideal for low-power applications

- Highly configurable IP offering fast system integration and reduced design risk and cost

- Low latency and high bandwidth for best system performance

- Support for a wide range of standards enables system flexibility for embedded and extended storage

- The IP ensures compatibility with previous and next generation SD standards

The SD Host Controller IP is developed in Verilog HDL and validated on multiple FPGA platforms including Xilinx, Intel, Lattice, and Microchip. Check out the resource utilisation document for more information.

The SD Host Controller IP is available in two variants

- Simplified Bare-metal driver for non-SoC FPGA devices

- FPGA vendors support bare-metal SD drivers on their soft cores to configure the registers using the AXI4-lite interface, while the AXI4-MM interface is used for data transfer in DMA mode

- Bare-metal SD driver supports the SD card initialization and basic write/read operations required for proving the IP functionality

- Linux Driver for SoC devices

- Linux SD driver running on the Arm cores supported by SOC devices will configure the registers using the AXI4-lite interface and the AXI4-MM interface is used for the data transfer in DMA mode

- User can perform all operations such as mount, patriation, and other operations supported by the standard Linux driver

iWave offers a complete IP solution for its SD/SDIO Host Controller IP consisting of RTL code or netlist, synthesis scripts, test environments, and comprehensive documentation, all backed by its world-class customer support.