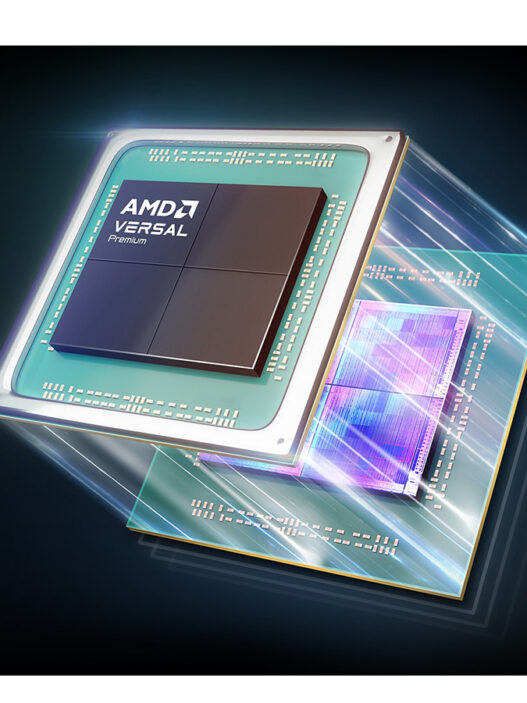

Delivering cost and power-efficient performance for a wide range of I/O-intensive applications at the edge, Spartan UltraScale+ devices offer the industry’s highest I/O to logic cell ratio in FPGAs built in 28nm and lower process technology, deliver up to 30% lower total power consumption versus the previous generation, and contain the most robust set of security features in the AMD Cost-Optimised Portfolio.

“For over 25 years the Spartan FPGA family has helped power some of humanity’s finest achievements, from lifesaving automated defibrillators to the CERN particle accelerator advancing the boundaries of human knowledge,” said Kirk Saban, corporate vice president, Adaptive and Embedded Computing Group, AMD. “Building on proven 16nm technology, the Spartan UltraScale+ family’s enhanced security and features, common design tools, and long product lifecycles further strengthen our market-leading FPGA portfolio and underscore our commitment to delivering cost-optimised products for customers.”

Flexible I/O interfacing and power efficient compute

Spartan UltraScale+ FPGAs are optimised for the edge, delivering high I/O counts and flexible interfaces which allow the FPGAs to seamlessly integrate and efficiently interface with multiple devices or systems to address the explosion of sensors and connected devices.

The family offers the industry’s highest I/O to logic cell ratio of FPGAs built on 28nm and below process technology, with up to 572 I/Os and voltage support up to 3.3V, enabling any-to-any connectivity for edge sensing and control applications. The proven 16nm fabric and support for a wide array of packaging, starting as small as 10x10mm, provide high I/O density in an ultra-compact footprint. The extensive AMD FPGA portfolio also provides the scalability to start with cost-optimised FPGAs and continue through to midrange and high-end products.

The Spartan UltraScale+ family is estimated to offer up to a 30% reduction in power compared to the 28nm Artix 7 family, through 16nm FinFET technology and hardened connectivity. They are the first AMD UltraScale+ FPGAs with a hardened LPDDR5 memory controller and PCIe® Gen4 x8 support, providing both power efficiency and future-ready capabilities for customers.

State-of-the-Art security features

Spartan UltraScale+ FPGAs offer the most state-of-the-art security features in the AMD Cost-Optimised FPGA portfolio.

- Protecting IP: Support for Post-Quantum Cryptography with NIST-approved algorithms offers state-of-the-art IP protection against evolving cyber-attacks and threats. A physical unclonable function provides each device with a unique fingerprint for added security.

- Preventing tampering: PPK/SPK key support helps manage obsolete or compromised security keys while differential power analysis helps protect against side-channel attacks. The devices contain a permanent tamper penalty to further protect against misuse.

- Maximising uptime: Enhanced single-event upset performance helps fast and secure configuration with increased reliability for customers.

The entire AMD portfolio of FPGAs and adaptive SoCs are supported by the AMD Vivado Design Suite and Vitis Unified Software Platform, allowing hardware and software designers to leverage the productivity benefits of these tools and included IPs via a single designer cockpit from design to verification.

AMD Spartan UltraScale+ FPGA family sampling and evaluation kits are expected to be available in the first half of 2025. Documentation is available today with tools support starting with the AMD Vivado Design Suite in the fourth quarter of 2024.