Achieving a switching energy below 100 femto-Joule per bit and >1015 endurance, these breakthrough results bring non-volatile SOT-MRAM technology a step closer to last-level cache memory applications.

SOT-MRAM is a promising candidate for replacing SRAM as a last-level cache memory in high-performance computing (HPC) applications. Just like SRAM, it offers a high switching speed (in the sub-ns regime) and promises unlimited endurance. Moreover, being nonvolatile, SOT-MRAM bit cells achieve lower standby power than SRAMs at high cell density. Also, SOT-MRAM bit cells can potentially be made much smaller than SRAM cells, translating into a higher bit packing density.

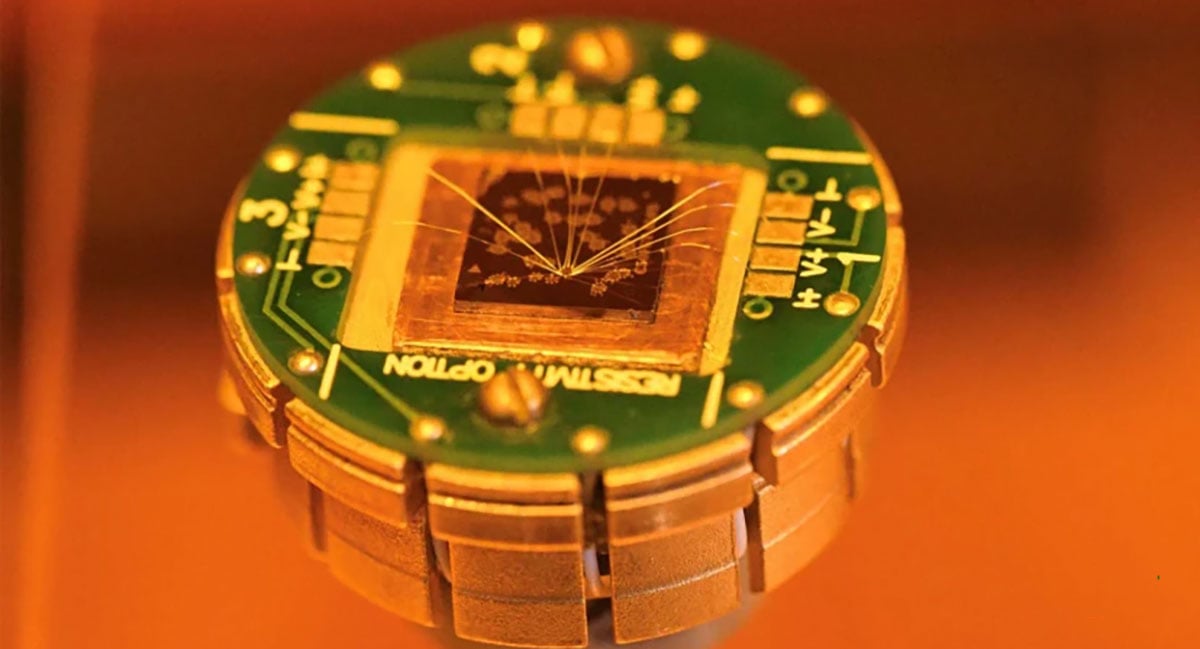

imec has experimentally explored the scaling potential and limitations of single perpendicular SOT-MRAM devices processed on 300mm wafers – the first ever reported study on SOT-MRAM device scalability. At IEDM 2023, they show that scaling the SOT track not only reduces the footprint of the SOT-MRAM cell, but also largely improves the cell’s performance and reliability.

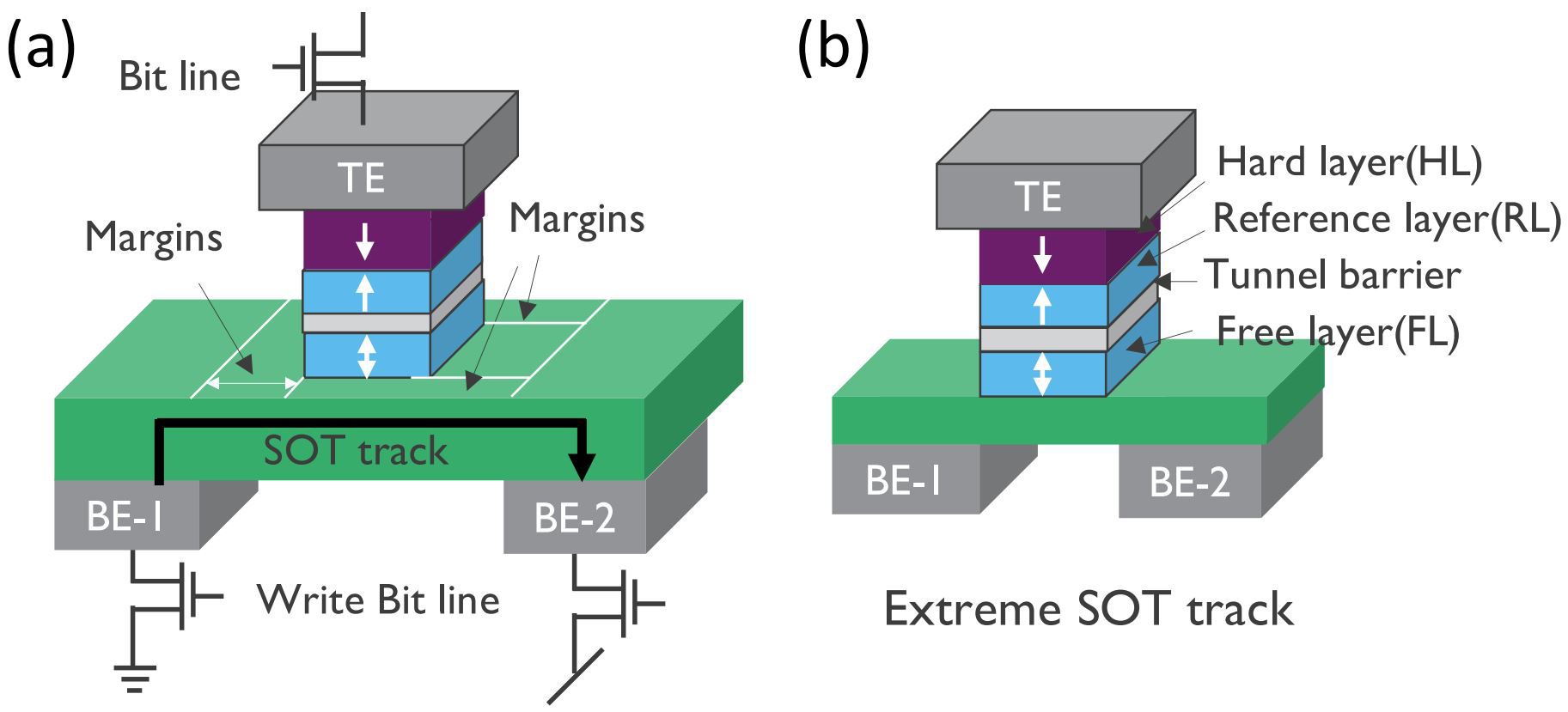

The SOT track is a layer made of metal such as tungsten (W) or platinum (Pt) that resides below the magnetic tunnel junction (MTJ) – the actual switching element of the SOT-MRAM device. The SOT track serves as an in-plane current injection layer, which has been introduced to de-couple read and write paths.

“In conventional SOT-MRAM designs, the area occupied by the SOT track is larger than the actual MTJ pillar footprint to provide sufficient margin for overlay process control,” explains Sebastien Couet, Program Director Magnetics at imec. “But this results in wasted energy, as part of the current flows outside the MTJ area. We scaled SOT-MRAM devices to their extreme, with SOT track and MTJ pillar having comparable dimensions (critical dimension ~50nm). For these devices, we observed a switching energy below 100 femto-Joule (fJ) per bit, i.e., a reduction of 63% compared to conventional designs. This helps address a remaining challenge of SOT-MRAM, which traditionally requires a high current for the write operation.”

On top of that, we showed that scaling the SOT track improves the memory’s endurance, as it reduces Joule heating inside the SOT layer.

Sebastien Couet: “With an endurance beyond 1015 program/erase cycles, we have experimentally validated our assumption that SOT-MRAM cells can have unlimited endurance – an important requirement for cache memories.”

“Our data provides valuable input for circuit designers to perform design-technology co-optimisation (DTCO) of SOT-MRAM technology at advanced nodes – trading of performance improvement and design margins. Future work focuses on material engineering to further reduce the switching energy per bit, and on optimising bit cell configuration to further shrink the cell area compared to SRAM. On the longer term, these learnings will also be transferred to the development of voltage-gated (VG) SOT-MRAM multi-pillar devices – imec’s ultimate solution for high-density embedded memory applications,” adds Sebastien Couet.

Figure 1: (a) Schematic of a conventional SOT-MRAM architecture with margins in SOT track design; (b) the extreme SOT design with no margins.

Figure 2: TEM cross-sectional view of an extremely scaled SOT device. The SOT track has the same length as the MTJ cell.

Figure 3: Switching energy per bit of SOT-MRAM devices with varying margins for width or length. For an extremely scaled device, a switching energy below 100 femto-Joule (fJ) per bit is achieved.

.JPG)

.JPG)