Cadence speeds hardware and software verification

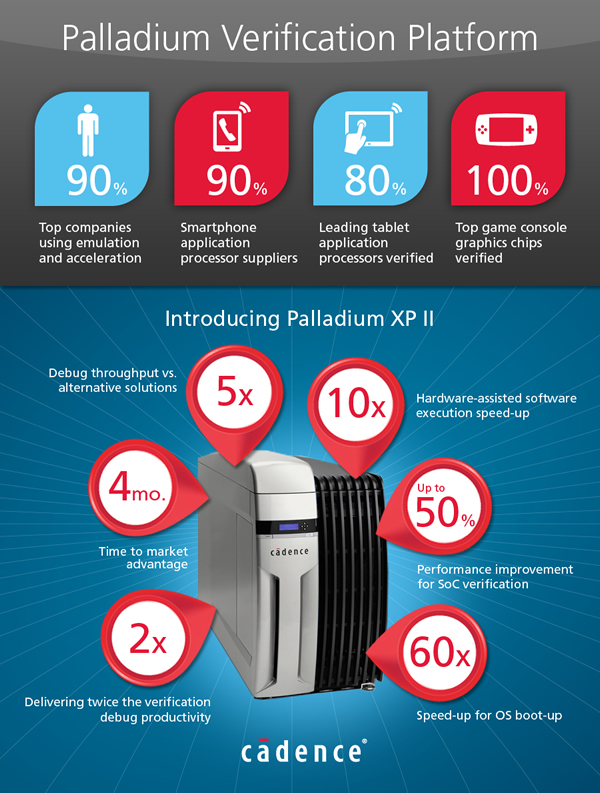

In an move to further reduce time to market for both semiconductor and system manufacturers, Cadence Design Systems has today introduced the Palladium XP II Verification Computing Platform as part of an enhanced System Development Suite, significantly speeding up hardware and software verification. The Palladium XP II platform builds on the award-winning Palladium XP emulation technology by boosting verification performance by up to 50% and extending its industry-leading capacity to 2.3 billion gates.

With reduced power and increased gate density, customers can now run larger payloads in a smaller footprint, reducing overall cost of ownership. Cadence has also added support for eight new mobile and consumer protocols for simulation acceleration.

Given the growing need for early, fast, and accurate hardware/software verification, Cadence expanded the capabilities of its System Development Suite centered around Palladium, adding:

- Patent-pending hybrid technology, which combines the Cadence Virtual System Platform with the Palladium XP series to deliver up to 60X speed-up for embedded OS verification and 10X performance speed-up for hardware/software verification,

- Embedded test bench for advanced virtualization of system environments, enabling users to verify peripheral software drivers prior to tape-out, resulting in faster post-silicon bring-up.

Gary Smith, chief analyst at GSEDA, comments: “In our latest update of the highly contested Transaction Based Acceleration market for 2012 Cadence continues to be the market leader. The new upgraded hardware capabilities of Palladium XP II platform and the additional advanced use models position Cadence well to address the ever increasing system to verification challenges users are facing.”

“With the Cadence Palladium Virtual System Platform hybrid solution, we experienced up to 60X speed-up of OS bring-up over pure in-circuit emulation combined with up to 10X performance improvement for production and test software executing on top of the OS interacting with accurate hardware representations in the Palladium platform,” said Narendra Konda, director of engineering at NVIDIA. “This new use model significantly improves NVIDIA’s system software validation cycle and ensures a smoother post-silicon bring-up.”

“Using the Palladium platform and its embedded test bench use model, we uncovered critical issues and resolved them prior to tape out, using models of peripheral devices that are connected to the SoC as part of a fully synthesizable embedded test bench,” said Vahid Ordoubadian, director of IC Engineering, Mobile Platform Solutions at Broadcom Corp. “As a result, we experienced faster bring-up for a new SoC architecture and were able to run initial tests in less than a day.”

“Our ability to offer production-level software along with our SoC is key to our time to market goals, because we do not ramp revenue until that software is ready,” said Kent Goodin, executive vice president of engineering at Zenverge. “The Palladium XP II platform allows our software teams to develop production-worthy code prior to the IC’s mask release and arrival of the prototype. This has allowed Zenverge to engage with customers at least six months earlier than would be possible without the co-development aspects of the Palladium XP II platform’s emulation solution.”