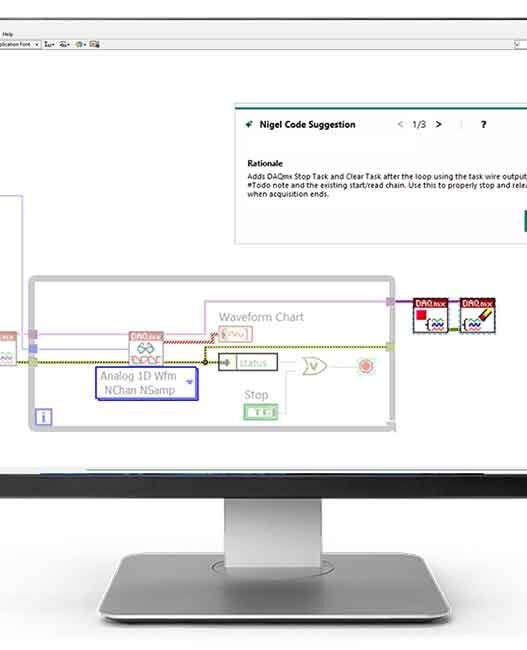

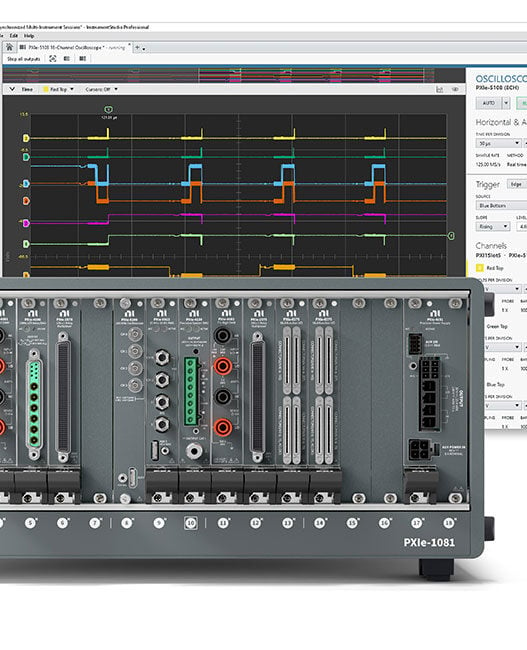

The instruction capture and display features of SourcePoint make the process much more intuitive because of the various views the developer has into code execution. For example, four different types of views – code, trace, branch and chart – give developers the ability to easily visualise code execution even when code is running on multiple cores. All four views are synchronised to simplify moving from one view to another. The root causes of bugs like performance bottlenecks or execution ordering problems can be quickly visualised for further analysis by the software developer. In addition, timestamps accurate to a particular processor cycle are provided by SourcePoint.

To serve the needs of different types of design teams working on a wide range of applications, two ASSET Arium hardware modules support the SourcePoint debugger. The ECM-XDP3 is a run-control probe capable of configuring and accessing trace data and storing it on-chip or on the target platform.

Another hardware module, the LX-1000 Trace Port Analyser, has 2Gbytes of memory where trace results can be stored off-chip. Software and firmware engineers can examine the trace results using the analyser to identify the precise location of the cause of a bug. Analytical capabilities such as statistical tabulation and others are synchronised with SoucePoint’s line-by-line code display of trace results.