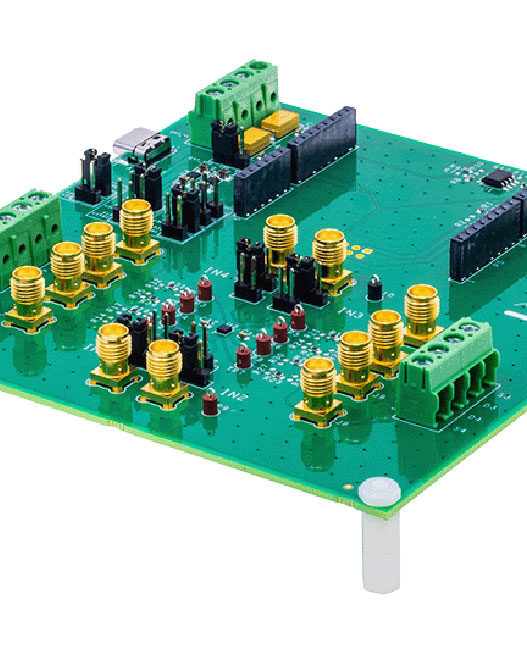

Renesas is offering 11 clock buffers and four multiplexers. The devices, which also support and provide extra margin for PCIe Gen5 implementations, complement Renesas’ low-jitter 9SQ440, 9FGV1002 and 9FGV1006 clock generatorsto offer customers a complete PCIe Gen6 timing solution for data centre/cloud computing, networking and high-speed industrial applications.

The PCIe Gen6 standard supports high data rates of 64GT/s while requiring low clock jitter performance of less than 100fsRMS. Renesas’ RC190xx clock buffers and RC192xx multiplexers have PCIe Gen6 additive jitter specs of only 4fs RMS, making them virtually noiseless, and thereby future-proofing customer designs for the next generation of industry standards.

“PCIe Gen6 timing will be at the heart of new equipment in data centers, high-speed networking and other applications,” said Zaher Baidas, Vice President of the Timing Products Division at Renesas. “As we have done for preceding generations, Renesas is providing customers with the first timing solution to enable these new, higher-performance systems. Our customers know that we have the technical expertise and market knowledge to ensure that their products will be able to meet future requirements as well.”

“By delivering the first discrete timing solution for PCIe Gen6, Renesas is enabling customers to develop the next-generation of high-performance systems,” said Rich Wawrzyniak, Principal Analyst for Semico Research. “It will be interesting to see the innovative implementations that result from this new capability, especially when considering how solutions for the emerging Chiplet market are starting to evolve, with the need for increasing speed and bandwidth as an underlying constant.”

Key features of Renesas’ PCIe Gen6 clock buffers and multiplexers

- Low 4fs PCIe Gen6 additive jitter, 1.4ns in-out delay, 35ps out-out skew, and -80dB Power Supply Rejection Ratio (PSRR) @100kHz easily ensure robust system design

- 30% space-saving compared to earlier devices

- Selectable SMBus addresses allow easy use of multiple devices

- SMBus write-protect feature enhances system security

- Loss-Of-Signal (LOS) output supports system monitoring and redundancy

- 4-wire Side-Band interface supports high-speed serial output enable/disable and device daisy-chaining

- Power Down Tolerant (PDT) and Flexible Start-up Sequencing (FSS) features ensure good behavior under abnormal system conditions