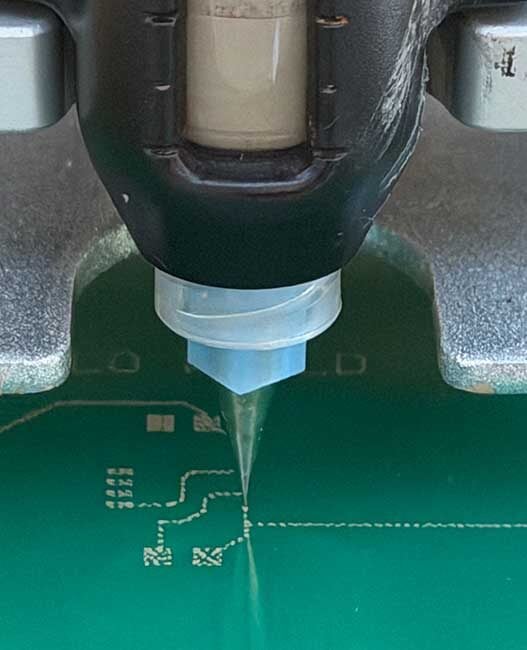

Leading customers, including CEVA, Faraday Technology Corporation, and HiSilicon Technologies have reduced their verification schedules from months to weeks and are successfully implementing the most advanced ARM technology using Cadence VIP for AMBA protocols, part of the company’s comprehensive VIP Catalog for SoC verification.

Cadence has worked closely with ARM to ensure its VIP solutions support ARM CoreLink CCI-400 Cache Coherent Interconnect and CoreLink NIC-400 Network Interconnect using the AMBA 4 protocols. As a result, mutual ARM and Cadence users benefit from a proven, flexible and highly differentiated verification solution for ARM CoreLink interconnect IP.

“As the complexity of ARM partners’ designs increases year after year, successfully verifying the performance of the SoCs has become a critical imperative,” said Joe Convey, director of design enablement at ARM. “The comprehensive Cadence verification IP solution for AMBA protocols has enabled our mutual customers to address this challenge while incorporating the latest ARM technology. ARM’s partnership with Cadence helps customers achieve continued success as they roll out next-generation designs incorporating our most advanced AMBA specifications such as AXI4 and AXI Coherency Extensions (ACE).”

Cadence VIP Catalog includes simulated, assertion-based and accelerated VIP for the ubiquitous AXI, AHB, and APB protocols. In addition, Cadence VIP supports AMBA 4, the latest addition to the AMBA family, which adds five new interface protocols: ACE for full cache coherency between processors; ACE-Lite for I/O coherency; AXI4 to maximize performance and power efficiency; AXI4-Lite and AXI4-Stream ideal for implementation in FPGA. Designers of IP, sub-systems and SoCs based on ARM protocols have seen dramatic improvements in design quality and time to market by using the full range of verification IP offered by Cadence.

“CEVA is the world’s leading licensor of DSP cores and platform solutions for the mobile, digital home, and networking markets. Our proprietary FIC bus delivers the right balance of features needed to deliver optimized designs,” said Richard Kingston, director of marketing and investor relations, CEVA, Inc. “The flexible Cadence VIP for AXI gives us the ability to adapt it to our unique application and exhaustively verify the bus interconnects. This cut our verification effort from 6 months to 3 weeks.”

Cadence’s commitment to making verification IP available when, or even before the delivery of new specifications, was demonstrated by the company’s collaboration with ARM to help productize the ACE specification, and support for all of the early customers for the ARM Cortex-A15 processor. This early collaboration means that mainstream adopters of ACE can proceed with confidence using the proven Cadence VIP for ACE.

“HiSilicon is a leader in ASICs and solutions for communication networks and digital media. Delivering advanced multi-core ARM SoCs to our customers requires leading IC design technologies,” said Ting Lei, director of Cloud Computing Department, HiSilicon. “The Cadence VIP for AXI4 and ACE enables us to quickly and efficiently deliver bug-free SoC designs.”

“As a leading ASIC and SIP, silicon intellectual property provider, Faraday has been committed to enabling customers to realize their ideas in silicon in a timely manner. We adopted the Cadence VIP solution for its maturity, full-feature set and support. With the adoption, Faraday can provide customers with comprehensive SoC and IP level verification coverage,” said Ken Liao, RD associate vice president at Faraday