MIPS OCI works seamlessly with the new Codescape MIPS software development kit (SDK) and new Codescape SysProbe technology to create a seamless and efficient debug environment for next-gen designs. Today’s increasingly complex chips present new debug challenges with SoCs containing many CPU cores and clusters and often multi-threading capabilities. MIPS OCI is designed to enable customers to quickly access these many-core, many cluster CPU designs through a highly parallel approach, leading to fast chip-bring-up and very efficient software development, integration and debug.

Daniel Mandell, IoT & embedded technology market research analyst, VDC Research, says: “Debugging is a non-trivial effort for embedded designers, comprising a large percentage of total design time. It becomes even more complex with today’s multi-core, multi-cluster CPU designs. Imagination’s new debug environment for MIPS is a significant development in that it enables companies to more quickly integrate and debug a MIPS CPU in their SoC design, whether as a management controller or a cluster of data processors in heterogeneous CPU designs. This debug advantage in combination with Imagination’s developer ecosystem puts MIPS in a unique position among CPU architectures.”

Jim Nicholas, Vice President of MIPS business operations, Imagination, says: “For our customers who are creating complex chip designs, our new debug environment for MIPS dramatically simplifies integration and debugging. And for potential customers who want to try a MIPS CPU in their SoC design alongside another company’s CPU, they can do so with the lowest possible risk and impact on their debug process. We believe this is a significant step in taking MIPS to the next level and breaking into new designs. With this move, we are alleviating any barriers for companies to choose MIPS.”

MIPS OCI represents a new modular approach to debugging MIPS systems that enables customers to employ the specific configuration needed for their design. It allows flexible probing of cores, and the combining of trace into a single flow. Advanced power management features let users power down CPU cores and clusters without any impact on other CPU cores that are still powered on and without breaking the JTAG chain. It enables breakpoint and trace configuration as well as on-chip data collection and global state access in multi-cluster systems, without halting the core.

MIPS OCI is included in the newest MIPS Warrior CPUs including the entry-level M-Class M6200, 64-bit multi-threaded I-Class I6400, and high-performance 64-bit P-Class P6600 CPUs and is backward compatible through JTAG to previous generations of MIPS CPUs. With the ability to interface to third party debug environments, MIPS OCI is designed to support a range of heterogeneous SoC designs.

For advanced multi-core, multi-cluster designs incorporating mid-range and high-end MIPS I-Class and P-Class CPUs, MIPS OCI includes JTAG / cJTAG / AMBA Advanced Peripheral Bus (APB) interfaces for maximum design flexibility. The system consists of a Debug Unit with dedicated memory and a register (ring) bus which connects the cores and global subsystems of a coherent system. For entry-level M-Class CPUs, an APB interface allows connection to a MIPS Debug Hub (MDH) or other debug access hardware.

Codescape SysProbes, based on a new probe design from Imagination, allow fast and efficient debug without requiring an intrusive software monitor or additional target I/O resources, by taking advantage of the advanced on-chip debug and trace features in MIPS IP cores. SysProbes are designed for use on coherent cluster/multi-cluster systems and are designed to offer simultaneous debug of heterogeneous SoC designs.

Codescape SysProbes provide a full debugging feature set including software and hardware breakpoints, hardware triggers, reset control, power monitoring, code profiling and much more. These features provide the requisite tools to meet the needs of today’s cutting edge development teams for first silicon bring-up, hardware and software development, debug and verification activities.

SysProbes are tightly integrated with the Codescape MIPS SDK. Interfaces include Codescape GUI based debugger with full RTOS awareness for the most prevalent RTOSes; and the Codescape Console, a command line interface suitable for low-level debug including silicon bring-up.

Codescape SDK is designed to provide everything needed for MIPS software development across the entire product lifecycle. The SDK supports software development, debug and optimisation prior to first silicon. When silicon is available the SDK provides extensive support for chip bring-up, software/hardware integration and application development. The latest version includes support for Release 6 of the MIPS32 and MIPS64 architectures and the microMIPS code compression architecture.

Codescape MIPS SDK Essentials (MIPS SDK) and Codescape MIPS SDK Professional (MIPS proSDK) offer powerful capabilities for developers targeting MIPS-based platforms from entry-level development boards to high-end multi-core systems. The Codescape MIPS SDK includes all the tools and resources needed to get started with MIPS software development. The Codescape MIPS proSDK is a premium, feature-rich toolkit that provides professional software developers all the tools needed for advanced MIPS software development.

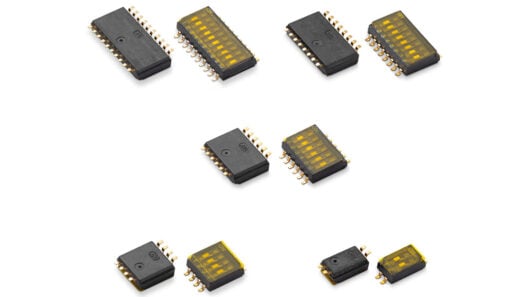

In addition to working with the new Codescape SysProbes, the MIPS SDK and MIPS proSDK work with a wide range of probes available from both Imagination and third parties. This includes high-end probes from Lauterbach and Green Hills Software, as well as the affordable MIPS Bus Blaster V3c for cost sensitive applications, students and hobbyists.