“As chip designers are tasked with developing increasingly complex products with tight time-to-market deadlines, having quick and easy access to design teams and resources both locally and globally creates a real competitive advantage,” said Simon Floyd, Director, Innovation and Product Lifecycle Management Solutions at Microsoft. “The Cadence PCB design tools, integrated with SharePoint, provide a unique environment that promotes team collaboration, design creation and control, and significant productivity improvements.”

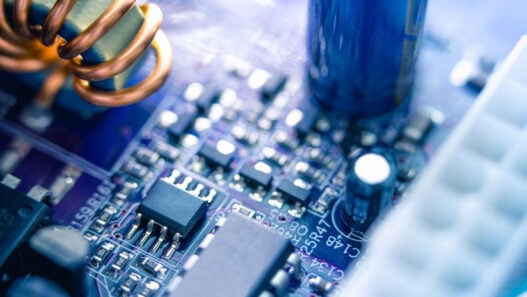

New features in the Allegro 16.6 product line enable enhanced miniaturization capabilities for embedding dual-sided and vertical components, timing-aware physical implementation and verification that accelerate timing closure, and improved ECAD and mechanical CAD co-design — all crucial for accelerating development of feature-rich electronic products.

The Allegro suite’s leading PCB design miniaturization capabilities were first introduced in 2011. The Allegro 16.6 product suite continues to leverage the latest manufacturing advances in embedding active and passive components to address the specific design requirements associated with ever shrinking board size. Components can now be embedded vertically on an inner layer of a PCB leveraging the Z-axis, which greatly reduces X- and Y-axis real estate on the board.

“Our leading ECP(C) technology meets customer needs for cost-effective miniaturization of PCBs,” said Mark Beesley, COO of Advanced Packaging at AT&S. “Cadence and AT&S have been partnering together for a number of years now addressing our joint customers’ needs for advanced miniaturization techniques.”

Allegro 16.6 accelerates timing aware physical implementation through Auto-interactive Delay Tuning. Auto-interactive Delay Tuning lessens the time to meet timing constraints on advanced standards-based interfaces, such as DDR3, by 30-50 percent. AiDT allows users to rapidly adjust the timing of critical high-speed signals on an interface-by-interface basis, or apply it at byte-lane level, reducing the need to tune the traces on a PCB from days to hours. The EMA Timing Designer, integrated with the Allegro PCB SI capability, helps users quickly achieve timing-closure on critical high-speed signals.

PCB/enclosure co-design is streamlined through an ECAD-MCAD flow based on EDMD schema version 2.0, a proStep iViP standard. This flow reduces unnecessary iterations between ECAD and MCAD teams shortening time for product creation.