An ACAP is well suited to accelerate a broad set of applications in the emerging era of big data and Artificial Intelligence. These include: video transcoding, database, data compression, search, AI inference, genomics, machine vision, computational storage and network acceleration.

Software and hardware developers will be able to design ACAP-based products for end point, edge and cloud applications. The first ACAP product family, codenamed ‘Everest’ will be developed in TSMC 7nm process technology and will tape out later this year.

“This is a major technology disruption for the industry and our most significant engineering accomplishment since the invention of the FPGA,” said Victor Peng, President and CEO of Xilinx.

“This revolutionary new architecture is part of a broader strategy that moves the company beyond FPGAs and supporting only hardware developers. The adoption of ACAP products in the data center, as well as in our broad markets, will accelerate the pervasive use of adaptive computing, making the intelligent, connected, and adaptable world a reality sooner.”

Acap technical details

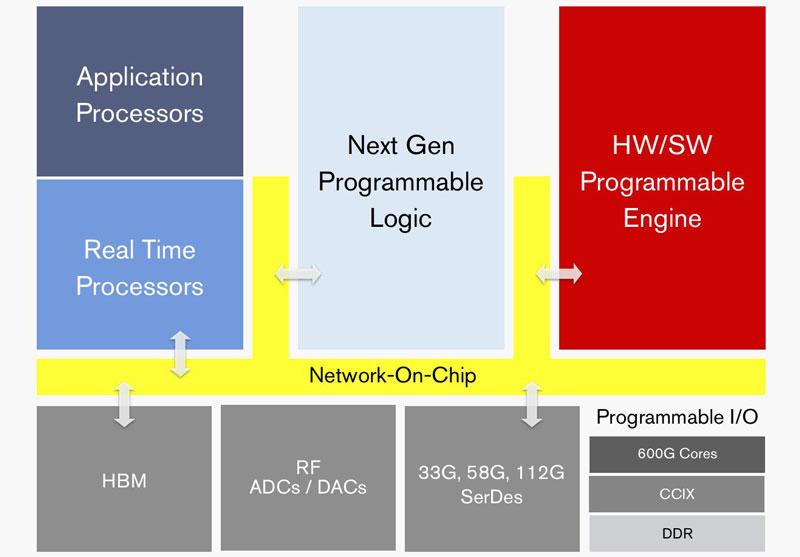

An ACAP has – at its core – a new generation of FPGA fabric with distributed memory and hardware-programmable DSP blocks, a multicore SoC, and one or more software programmable, yet hardware adaptable, compute engines, all connected through a Network on Chip (NoC).

An ACAP also has highly integrated programmable I/O functionality, ranging from integrated hardware programmable memory controllers, advanced SerDes technology and leading edge RF-ADC/DACs, to integrated High Bandwidth Memory (HBM) depending on the device variant.

Software developers will be able to target ACAP based systems using tools like C/C++, OpenCL and Python. An ACAP can also be programmable at the RTL level using FPGA tools.

“This is what the future of computing looks like,” said Patrick Moorhead, Founder, Moor Insights & Strategy. “We are talking about the ability to do genomic sequencing in a matter of a couple of minutes, versus a couple of days. We are talking about data centers being able to programme their servers to change workloads depending upon compute demands, like video transcoding during the day and then image recognition at night. This is significant.”

ACAP has been under development for four years at an accumulated R&D investment of over one billion dollars. There are currently more than 1,500 hardware and software engineers at Xilinx designing ‘ACAP and Everest’. Software tools have been delivered to key customers. ‘Everest’ will tape out in 2018 with customer shipments in 2019.

‘EVEREST’ performance improvements

Everest is expected to achieve 20x performance improvement on deep neural networks compared to today’s latest 16nm Virtex VU9P FPGA. Everest-based 5G remote radio heads will have 4x the bandwidth versus the latest 16nm-based radios.

A wide variety of applications across multiple markets like automotive; industrial, scientific and medical; aerospace and defense; test, measurement and emulation; audio/video and broadcast; and the consumer markets will see a significant performance increase and greater power efficiency.