At the 2025 IEEE International Electron Devices Meeting (IEDM), imec presents breakthrough performance of p-type FETs with monolayer WSe2 channels, and improved fab-compatible modules for source/drain contact formation and gate stack integration. These results, achieved through collaborations with leading semiconductor manufacturers, mark a significant advance for 2D-material-based technology, which is considered a promising long-term option for extending the logic technology roadmap.

Replacing Si conduction channels with atomically thin layers made of 2D transition metal dichalcogenides (MX2) promises to enable ultimate gate and channel length scaling, while maintaining good electrostatic channel control and high carrier mobility. Crucial milestones to be achieved include high-quality 2D-material layer deposition, gate stack integration, low-resistance source/drain contact formation, and 300mm fab integration. Also, while most efforts focus on improving n-type devices (with channels made of WS2 or MoS2), more fundamental work is needed on p-type devices, which require different channel materials (such as WSe2).

Sankar Kar, VP R&D Compute and Memory device technologies at imec: “At 2025 IEDM, we show in two separate presentations how in-depth collaborations with leading semiconductor manufacturers within imec’s core CMOS Industrial Affiliation Program (IIAP) have enabled breakthroughs in the performance of 2D-material-based devices. In both partnerships, combining high-quality 2D material layers provided by the manufacturer with imec’s optimised contact and gate modules played a key role in pushing the technology beyond state of the art.”

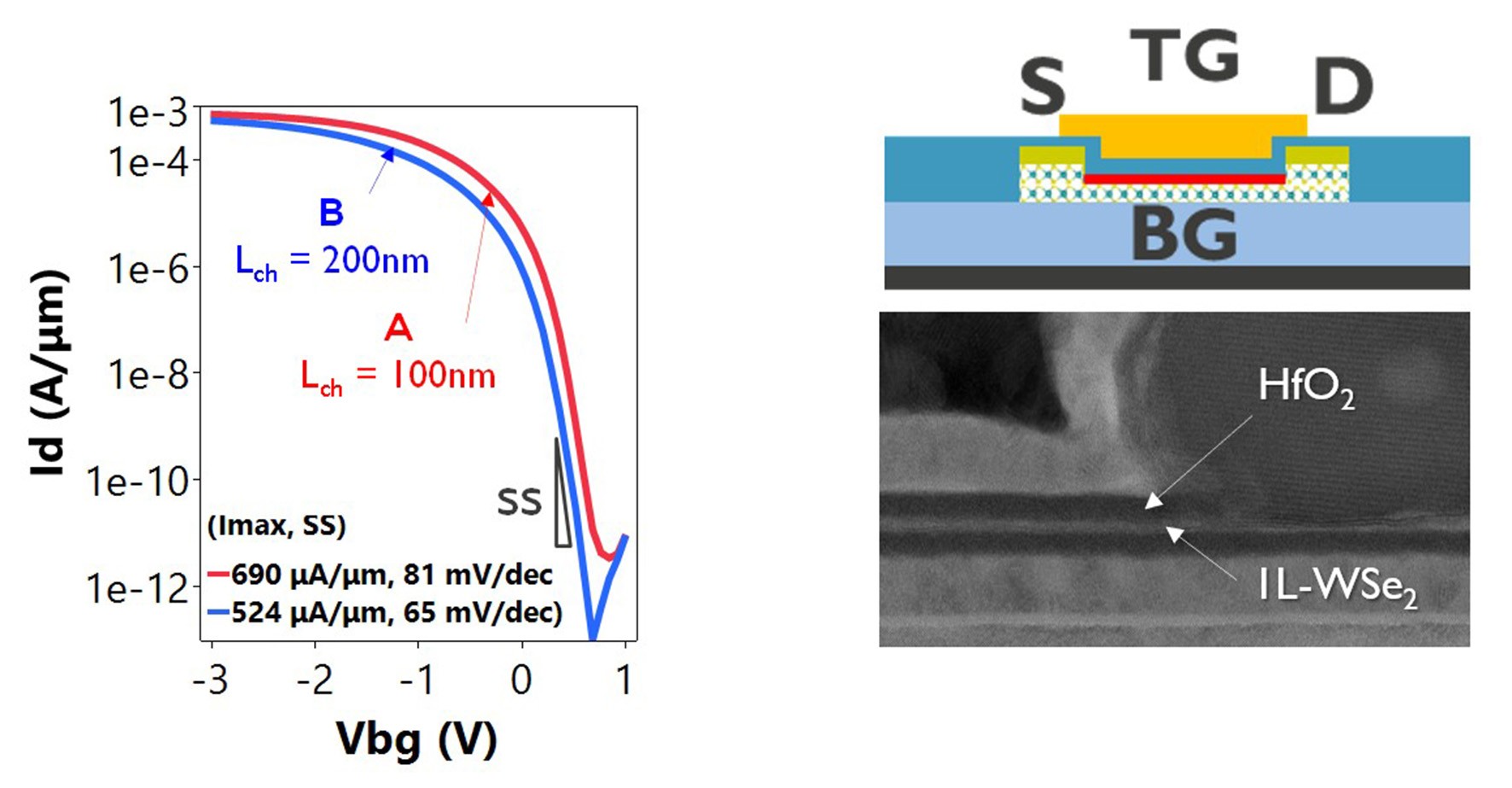

“Depositing the top-gate HfO2 dielectric on top of a MX2 channel requires an additional seed layer to support HfO2 nucleation and growth”, explains Sankar Kar. “For nFETs, this is solved by creating an AlOx interfacial layer, but this approach is challenging for pFETs due to the different characteristics of the WSe2 channel material as compared to its n-type counterparts. In partnership with TSMC, we started with a synthetic bilayer of WSe2, which was formed by subsequently transferring two high-quality WSe2 monolayers from TSMC on our substrates. We then oxidised the top WSe₂ monolayer, converting it into an interfacial layer that successfully supported the deposition of the HfO₂ gate oxide. This fab-compatible lab-based integration approach resulted in record performance of our dual-gated pFETs.”

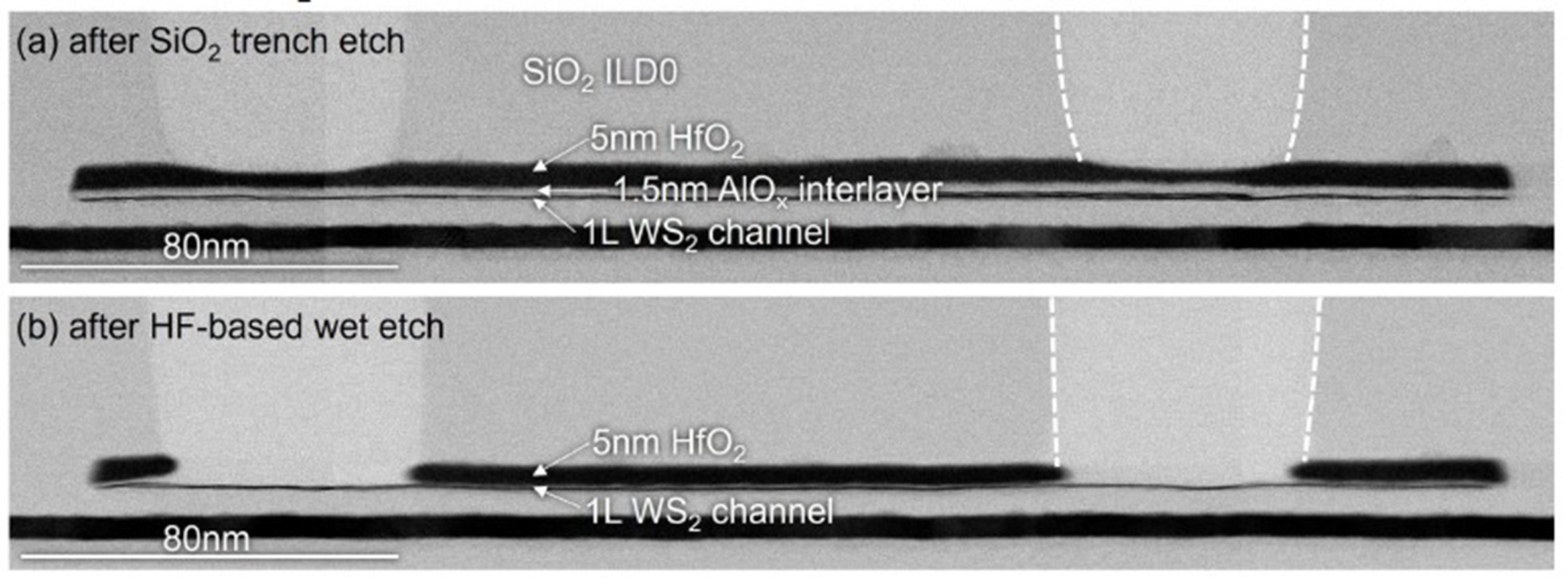

Another presentation highlights the collaboration between imec and Intel in developing 300mm manufacturable modules for source/drain contacts and gate stack integration, for n-type (WS2 and MoS2) and p-type (WSe2) 2D-FETs. “The key innovation consists in applying a selective oxide etch process on Intel’s high-quality 2D material layers, that were capped with an interfacial AlOx layer, a HfO2 layer and a SiO2 layer”, Sankar Kar explains. “The oxide etch process allowed the formation of fab-compatible damascene-style top contacts – a world first. In addition, during the vertical contact etch process, the interfacial AlOx layer was simultaneously etched laterally, removing AlOx from the channel region. This significantly lowered the top gate’s EOT, benefiting the gate’s transfer characteristics.”

This research was funded by the imec IIAP Exploratory Logic program, the 2D-PL pilot line project through Horizon Europe (101189797) and Horizon 2020 (952792) grant agreements.

Figure 1 – (Left) Transfer curves of 2D-pFET devices using defect-passivated synthetically-created bi-layer WSe2 films, with best device showing Imax = 690µA/µm; (right) TEM cross-section of finalized dual-gated 2D pFET (Lch=channel length TG=top gate; BG=back gate; S=source; D=drain; IL=interlayer), in collaboration with TSMC.

Figure 2 – (a) Trench dry etch into SiO2; (b) dry and wet etch selectively stopping on the monolayer WS2 channel, also causing AlOx interlayer lateral removal along the full channel length (in collaboration with Intel).