Keysight Technologies has unveiled a new PCIe 7.0 Receiver (RX) test application, extending its PCIe 7.0 portfolio to enable end-to-end transmitter and receiver validation.

The receiver test application addresses the growing challenge of validating receiver performance at 128GT/s for next-generation compute, AI, and data centre applications.

As cycles between PCIe base specification releases continue to shorten and the PCIe 7.0 standard moves toward adoption, engineers face increasing challenges in validating receiver performance.

These challenges are driven by a lack of test equipment dedicated to receiver testing, combined with increasingly complex stress signal calibration requirements.

At 128GT/s, PCIe 7.0 receiver validation has become a defining hurdle for the industry. Reliable validation testing is essential to reduce risk and ensure interoperability as the ecosystem scales. Keysight’s receiver test solution enables engineers to validate devices with confidence.

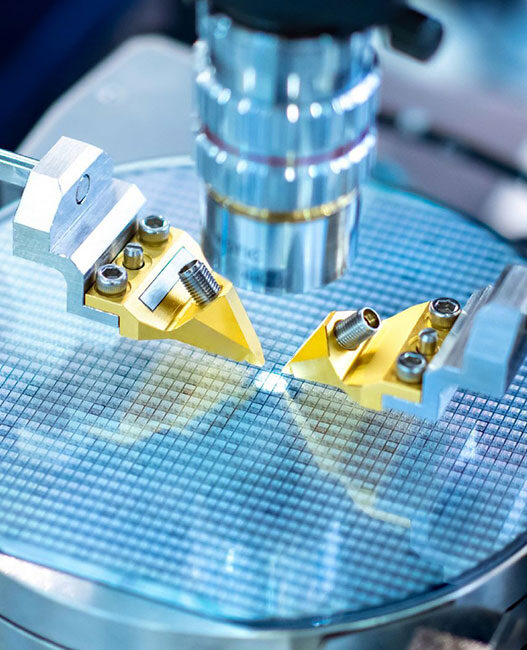

Keysight’s M8050A BERT family, combined with the M8042A 120 GBaud pattern generator and M8043A error analyser, meets the requirements for PCIe 7.0 receiver stress testing, enabling accurate signal generation and analysis for ASIC validation.

Complementing the hardware, the new N5991PB7A reduces setup effort and accelerates receiver validation by simplifying the calibration and control of PCIe 7.0 receiver stress signals.

Advanced automation capabilities enable more accurate and reliable ASIC receiver characterisation.

Together, the hardware and software provide a comprehensive PCIe 7.0 receiver test solution that streamlines validation workflows, improves measurement confidence, and supports reliable ASIC development in common clock mode.

The new receiver stress calibration for PCIe 7.0 accelerates receiver bring-up and validation and reduces compliant risk at 128GT/s.

Dr. Joachim Peerlings, Vice President of Network and Data Centre Solutions at Keysight, said: “PCIe 7.0 receiver validation at 128 GT/s is one of the industry’s most significant signal integrity challenges. By extending our PCIe 7.0 physical layer measurement portfolio with advanced receiver characterisation capabilities, we help customers reduce risk, accelerate development, and confidently validate next-generation ASIC designs.”

The PCIe 7.0 receiver test is being shown for the first time at the PCI-SIG Developers Conference in Santa Clara, California (6-7th May).