Effective PAM-8 signal processing requires a highly linear receiver system. To address this, researchers at Hanyang University have developed a multi-path architecture that enhances the linearity-power trade-off, doubling linearity with only a 20% increase in power. The design also achieves successful channel-loss compensation through a separated feed-forward equaliser path.

This technology enables an impressive 108Gb/s data rate, paving the way for faster, more energy-efficient, data-intensive applications.

High-voltage, higher-order PAM-8 signals are essential to achieve data rates beyond 100Gb/s, requiring highly linear receivers to maintain excellent signal-to-noise ratios.

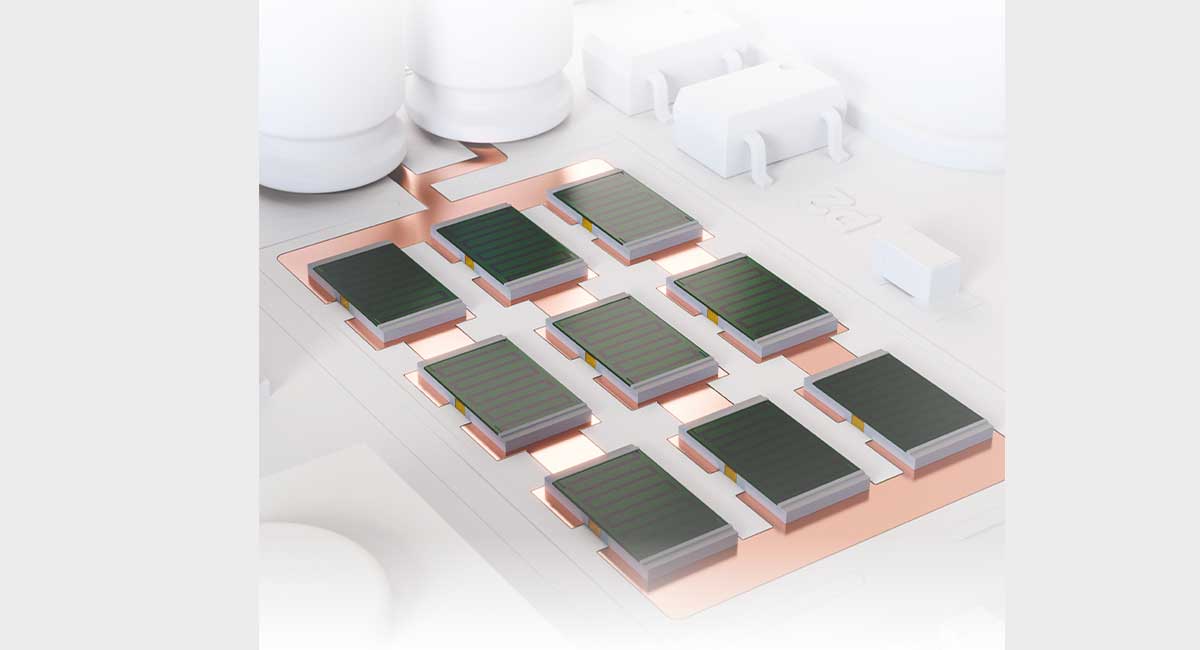

In a recent breakthrough work, a team of researchers, led by Mr. Sangwan Lee, an integrated M.S. and PhD degree student in electronic engineering, and Dr. Jaeduk Han, an Associate Professor of electronic engineering, at Hanyang University, South Korea, has proposed a multi-path architecture with enhanced linearity-power trade-off. The novel highly linear receiver frontend system with two-tap feed-forward equaliser (FFE) capability in 28nm CMOS exhibits a remarkable data rate of 108Gb/s and an input range of 1.4Vppd with 210.8mW total power and 1.95pJ/bit efficiency.

This next-generation technology was presented on 4th November at the IEEE Asian Solid-State Circuits Conference (A-SSCC), one of Asia’s premier semiconductor conferences.

Lee remarks: “In this research, we have maximised both power efficiency and signal processing capability through two unique architectures for processing ‘PAM-8’ signals, which are essential for next-generation high-speed communication.”

The researchers first dramatically improved the linearity-power trade-off through a ‘multi-path architecture.’ They designed the architecture by dividing the signal path, allowing each path to handle a sub-range of the total dynamic range. As a result, the number of required slicers or samplers was reduced, decreasing the load on the final stage and facilitating the achievement of remarkable efficiency: doubling the linearity with only 20% power increase.

Next, the team effectively compensated for channel loss through a ‘separated FFE path.’ Since high-speed signals suffer significant channel loss, compensation via an FFE is essential.

However, in conventional receiver architectures, the FFE must directly process large-voltage signals, leading to signal compression. The researchers designed a structure that completely separates the FFE path from the main path, allowing it to calculate the compensation value using only a small, attenuated signal. This approach fundamentally prevents compression, enabling successful channel loss compensation even while handling large input signals.

This technology is poised for immediate application as a core component in next-generation high-speed data communication infrastructure. Its key application areas include data centres and artificial intelligence (AI) clusters, wherein dramatically increasing the communication speed between servers can significantly facilitate the training of large-scale AI models and the processing of massive datasets, as well as next-generation networking equipment that forms the foundational technology for future 800G and 1.6T Ethernet systems.

Furthermore, the present research could help accelerate the computational speed of supercomputers used in advanced scientific research and simulations.

In the next five to 10 years, this work will serve as the foundational technology that accelerates the development of next-generation applications, including more powerful and widespread AI, the Metaverse, the AR/VR era, and sustainable data centres.

“It will provide the backbone for complex AI services like real-time translation, advanced medical diagnostics, and autonomous driving systems to become faster and more universally available. Moreover, by providing the massive bandwidth required for immersive virtual and augmented reality experiences, it will help make a seamless virtual world a reality. Lastly, as global data demand continues to explode, our power-efficient approach will help reduce the energy footprint of data centres, contributing to sustainable technological growth,” concludes Dr. Han.