In the world of robotics, the spotlight often falls on sensors, actuators, and artificial intelligence (AI) algorithms. Yet, beneath the surface, memory technology plays a pivotal, often underappreciated, role in enabling robots to perceive, decide, and act in real time. As robots become more intelligent and autonomous, the demands placed on memory systems have grown exponentially. Advances in memory, particularly DDR (Double Data Rate) technologies, have shaped the evolution of robotics, now making memory architecture a critical design consideration for roboticists.

The memory wall: a challenge for robotics

The concept of the ‘memory wall’ was introduced by William Wulf and Sally McKee in the 1990s to describe a growing bottleneck: processor speeds were increasing much faster than memory access speeds. For decades, this gap was a concern mainly for high-performance computing. Today, it has become a central challenge for robotics.

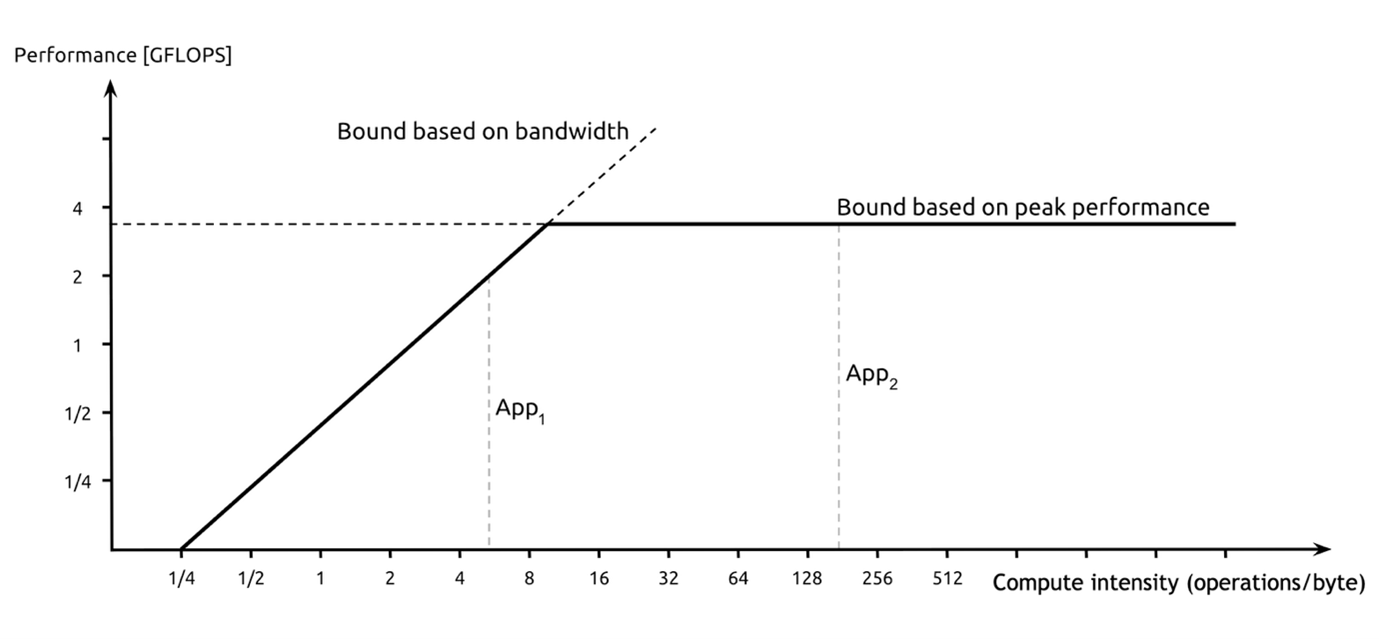

Robots, especially those powered by AI, must process massive streams of data from cameras, LiDARs, microphones, and other sensors. Tasks such as sensor fusion, real-time motion planning, and natural language understanding are data-hungry and memory-bound. When a robot’s processor must wait for data to arrive from memory, its reaction time suffers. This is a critical issue in applications ranging from autonomous vehicles to collaborative manufacturing robots.

The Roofline diagram captures the points at which a maximally efficient application will be memory- or compute-bound (Source: Wikipedia, CC License)

A brief history of DDR memory evolution

To understand how memory technology has risen to meet these challenges, it is helpful to trace the evolution of DRAM (Dynamic Random-Access Memory) and DDR standards. Early DRAM was asynchronous, with limited bandwidth and high latency. The introduction of synchronous DRAM (SDRAM) in the 1990s paved the way for the first DDR standard, which doubled data transfer rates by moving data on both the rising and falling edges of the clock signal.

Each subsequent DDR generation has delivered significant improvements:

- DDR (DDR1): introduced in 2000, doubled the data rate of SDRAM to 2.1–3.2GB/s per module

- DDR2: improved prefetch and lower voltage, reaching up to 6.4GB/s

- DDR3: increased data rates up to 12.8GB/s, with further reductions in power consumption

- DDR4: launched in 2014, supports up to 25.6GB/s per module, with enhanced reliability features

- DDR5: now mainstream, starts at 38.4GB/s and can exceed 51.2GB/s, with built-in error correction and higher efficiency

These advances have not only benefited servers and PCs but have also been crucial for embedded and mobile systems, which are key categories in robotics.

Robotics workloads: why memory matters more than ever

Modern robots are data-driven. Consider a service robot navigating a crowded shopping centre: it must simultaneously process high-resolution video, interpret speech, localise itself on a map, and plan safe, efficient paths – all in real time. Each of these tasks involves large, memory-intensive computations.

Sensor fusion, the process of combining data from multiple sensors to form a coherent understanding of the environment, is both compute- and memory-intensive. For example, fusing LiDAR point Clouds with camera images for object detection requires moving large datasets through memory at high speed. Latency in this process can mean the difference between a robot avoiding an obstacle or colliding with it.

![Bandwidth increases (GB/s) DDR1 through DDR5 [Chart: ServeTheHome]](https://www.electronicspecifier.com/wp-content/uploads/2025/09/Picture3-1.jpg)

Bandwidth increases (GB/s) DDR1 through DDR5 [Chart: ServeTheHome]

AI has become ubiquitous in robotics, powering everything from voice interfaces to object recognition. Deep neural networks, especially large models, are typically memory-bound: their performance is limited not by the speed of the processor, but by how quickly data can be fed from memory. As a result, memory bandwidth and latency are often the primary performance bottlenecks for AI inference in robots.

What is more, robots increasingly use multi-core processors and specialized AI accelerators. These architectures rely on high-bandwidth, low-latency memory to keep all cores and processing units fed with data. Memory contention and inefficient access patterns can cripple parallel performance, leading to sluggish or unpredictable robot behaviour.

Memory technologies for robotics: beyond DDR

While DDR (and its low-power variants, LPDDR) remain the mainstay for most robotic systems, other memory technologies are also making inroads:

- LPDDR4/LPDDR5: designed for mobile and embedded applications, these offer high bandwidth and low power consumption, a combination that is particularly important for battery-powered robots and drones

- HBM (High Bandwidth Memory): used in high-end AI accelerators, HBM stacks multiple memory dies vertically, providing massive bandwidth for demanding robotics workloads

- ECC (Error-Correcting Code): as robots are deployed in more safety-critical roles, ECC memory is increasingly important for reliability, and protecting against data corruption from radiation or electrical noise

Case studies: memory in action

Industrial robots

In manufacturing, robots are often required to process complex 3D vision data and execute precise, real-time control loops. Upgrading from DDR3 to DDR4 or DDR5 memory can halve the time required for image analysis and path planning, directly boosting throughput, efficiency and safety.

According to the latest preliminary figures from the International Federation of Robotics, in the US, the automotive industry is by far the leading industrial sector for the adoption of robots in manufacturing, installing around 14,000 robots annually.

Autonomous vehicles

Self-driving cars can be considered a type of robot and possess the core characteristics of robots: they perceive their environment through sensors, process information using AI, and make decisions to control their movement without direct human intervention. They are among the most memory-hungry robots, ingesting data from dozens of sensors and running multiple neural networks simultaneously. Here, memory bandwidth is a key determinant of how quickly the vehicle can react to changing road conditions. Increasing memory bandwidth reduces perception system latency substantially, translating to safer and smoother driving.

Service and social robots

Robots designed to interact with humans – whether in healthcare, hospitality, or retail – must process speech, gestures, and visual cues in real time. Memory upgrades not only improve response times but also enable more sophisticated AI models, making interactions more natural and engaging.

Practical design considerations

Selecting the right memory for a robotic system is a nuanced process. Designers must balance bandwidth, latency, power consumption, reliability, and cost and form factor.

![In 2024, the automotive industry installed more industrial robots than all other sectors combined in the US [Source: IFR]](https://www.electronicspecifier.com/wp-content/uploads/2025/09/Picture4-1.jpg)

In 2024, the automotive industry installed more industrial robots than all other sectors combined in the US [Source: IFR]

Higher bandwidth supports faster data movement, which is critical for AI and sensor fusion, and lower latency enables quicker reaction times. Power consumption is often an overriding consideration for mobile robots and drones, and error correction is central to reliability in safety-critical applications. Robots, in common with most other electronic systems, are likely to have strict space and budget constraints.

Workload analysis is key: a robot performing heavy AI inference may benefit most from high-bandwidth memory, while a simple delivery robot might prioritise low power.

The future: memory as a robotics enabler

As robots become more capable and autonomous, memory technology will only grow in importance. Emerging trends include:

- 3D-stacked and non-volatile memories that promise even higher bandwidth and persistence

- In-memory computing approaches, where computation is performed directly within memory chips, reducing data movement and latency

- AI-driven memory management for dynamic allocation and optimisation based on workload

Robotics is entering an era where the sophistication of memory subsystems may be as important as the choice of processor or sensor. Designers who understand and leverage the latest memory technologies will be best positioned to build the next generation of intelligent, responsive, and reliable robots.

Memory technology, especially the evolution of DDR and related standards, has quietly underpinned the rapid progress of robotics over the past two decades. As robots tackle ever more complex and safety-critical tasks, the need for high-bandwidth, low-latency, and reliable memory is greater than ever. By placing memory at the heart of system design, roboticists can unlock new levels of intelligence and performance.

By Jim Beneke, Vice President, Tria (an Avnet company)

This article originally appeared in the July’25 magazine issue of Electronic Specifier Design – see ES’s Magazine Archives for more featured publications.