The series achieves a high speed switching performance while keeping the low ON-resistance level of conventional DTMOS IV – all without loss of power. This is accomplished through the reduction of parasitic capacitance between Gate and Drain, (typical Ciss of 3000-6500pF) which also contributes to improved power efficiency and downsizing of products.

Gate pattern optimisation results in a 45% reduction in Gate-Drain charge (typical Qg of 65-135nC) when compared with conventional DTMOS IV. The product lineup features low ON-resistance (RDS(ON) MAX at VGS=10V of 0.088-0.040Ω) and the devices only suffer a small increase in low ON-resistance at high temperatures due to the use of the single epitaxial process. Drain current for the devices is in the range of 30.8-61.8A.

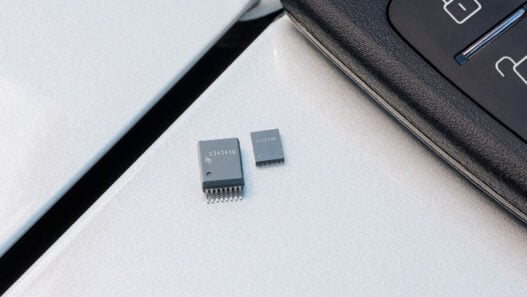

Using Toshiba’s state-of-the-art single epitaxial process, the DTMOS IV-H series is currently available in a T0-247 package, with additional package options, including 8x8mm DFN, TO-220 and TO-220SIS becoming available soon.