Custom-made motor control

How FPGA technology is being used in industrial applications to provide performance with flexibility, and to lower system costs. By Stefano Zammattio, Altera.

Designers of modern industrial systems face many challenges, including system complexity, changing standards, performance requirements, and reducing total system cost. Industrial system designers can choose to use FPGAs as coprocessors, intelligent I/O expanders (working alongside a separate processor device) or as a complete single chip SoC solution. The FPGA logic brings the ability to add support for new interfaces and high performance custom processing logic to the system, which can be modified at any time.

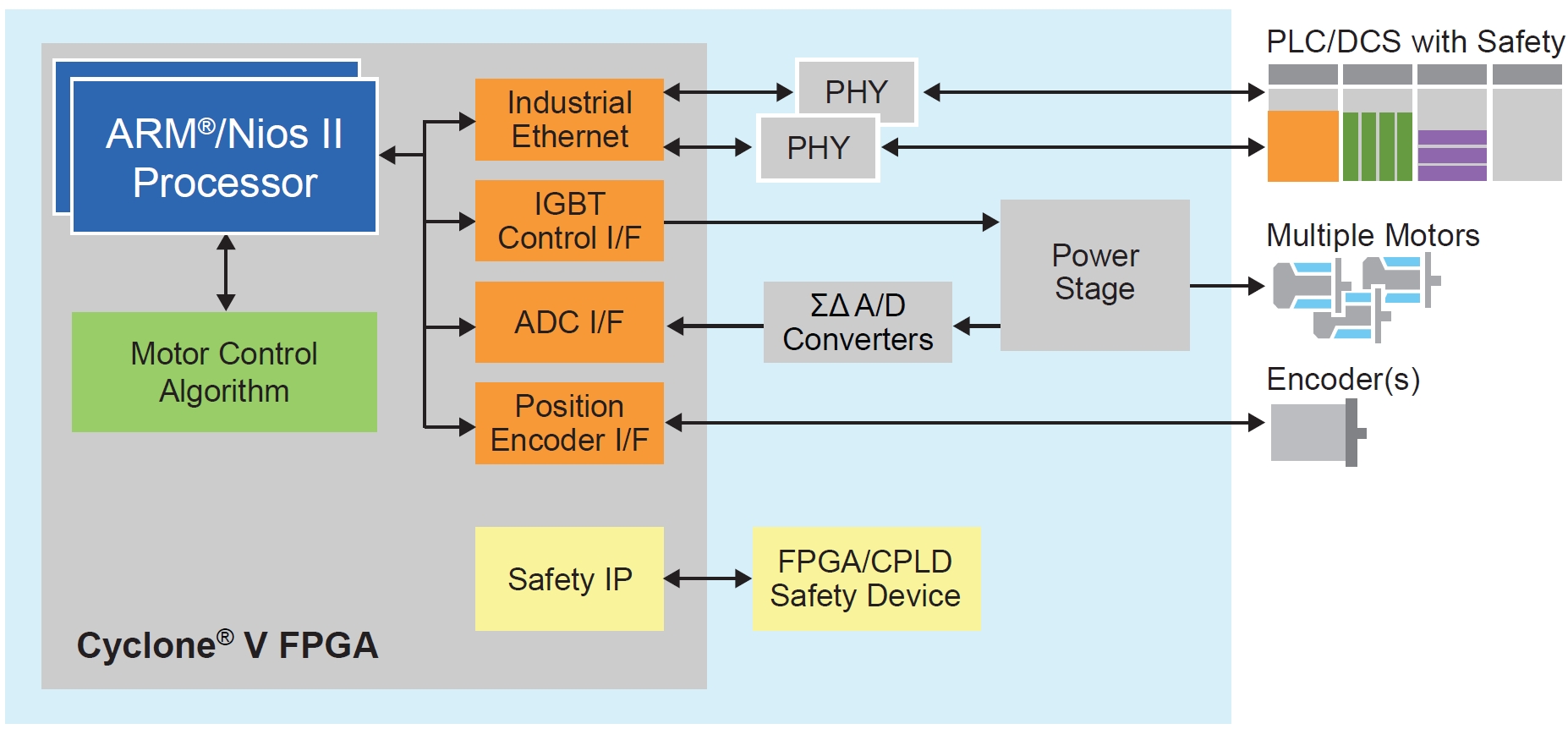

FPGA devices can contain soft processor cores (e.g. Altera’s Nios II processor) programmed into the FPGA logic, or they can contain a hard processor core as with the Altera’s Cyclone V SoC devices. In the Altera Cyclone V SoC devices the hard core is a dual core ARM Cortex-A9 that can run up to 925MHz. Figure 1 shows a typical FPGA based motor control system. The interface blocks in orange are implemented in FPGA logic, this means that you can implement any type of interface required by your system – and change it at any time using the Qsys graphical system design tool. This makes it easy to quickly create customised system solutions.

Using FPGA logic IP engineers can select between serial, parallel and sigma-delta ADC interfaces, different formats of digital encoder, customised PWM outputs to suit an IGBT or application, and choose between a wide range of industrial Ethernet or Fieldbus interfaces. All of this can be done without adding another device to the system and without an expensive board re-design. This also helps to future proof a design; if a standard changes or is replaced all that is needed is to modify and update the FPGA configuration.

Figure 1: FPGA based motor control system

If the MCU or DSP is required to run control, communications and system management task concurrently they often run out of processing bandwidth. With an FPGA a team could simply add a second soft processor or leverage the huge power of the Cortex-A9 hard processors that come at a very modest additional cost in the SoC devices. Even if there is a requirement that fully utilises the power of the hard processor core, teams can always implement a soft Nios II processor core to support the motor control while the Cortex-A9 runs an operating system or whatever high performance software processing the system requires.

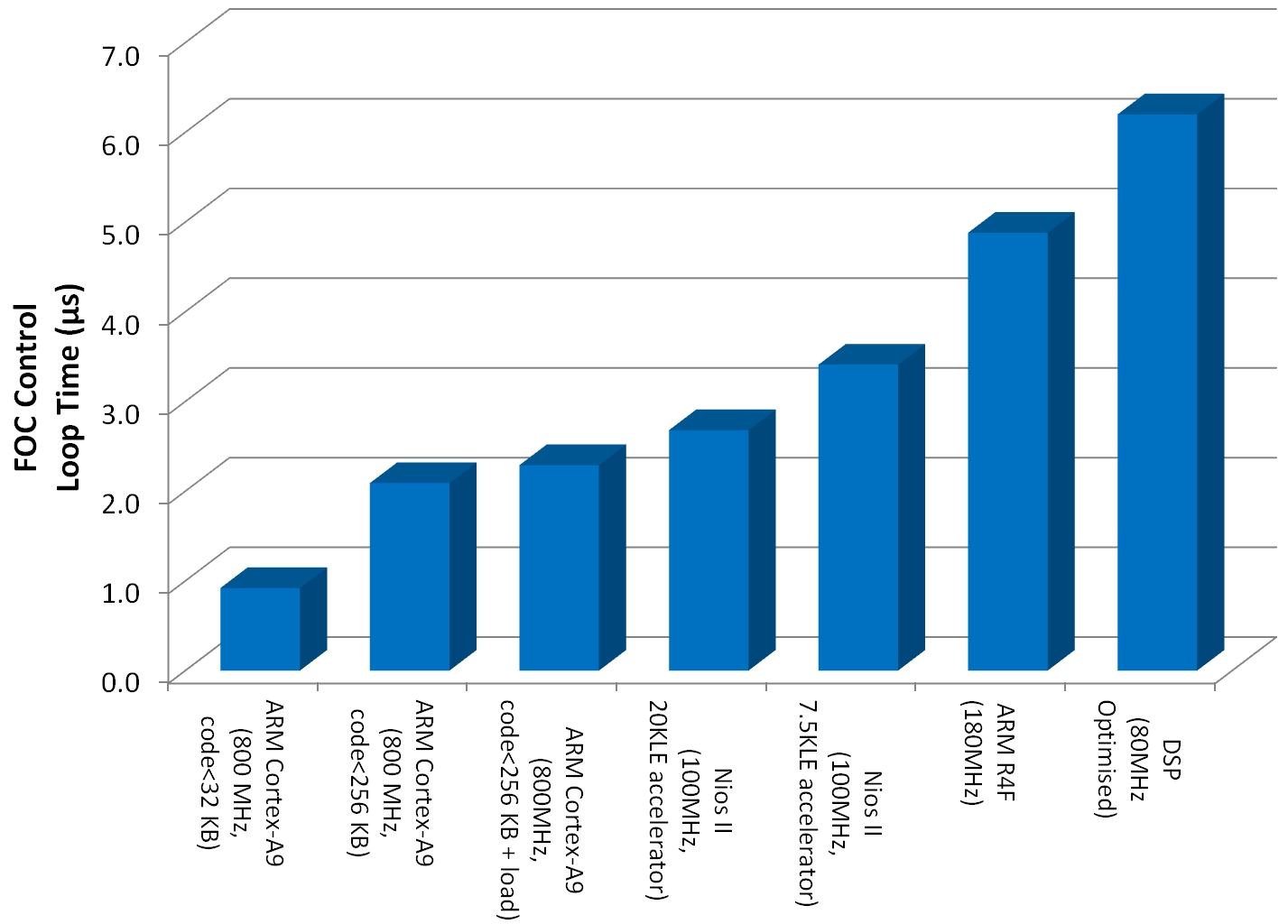

The green block in Figure 1 is a hardware acceleration module designed to greatly increase the performance of the Nios II processor for field orientated (motor) control algorithms. Figure 2 shows some typical performance data for a range of different solutions; as can be seen the Cortex-A9 and accelerated Nios II can deliver greater performance compared to traditional solutions.

The value proposition

Traditional solutions, however, are adequate if all that is needed is a simple motor control solution; the value of the FPGA is in reducing the system cost through integration and addition of flexibility to easily support a wide range of interfaces in any combination at design time and post production. The addition of the ARM Cortex-A9 in the SoC devices brings this value to a new level, as now a single FPGA device can also offer the ability to support the core processing functions of the system that often run on operating systems like Linux, Windows Compact or VxWorks.

Figure 2: FOC control loop performance for different systems

A second area where the FPGA brings significant advantage is performance. If a motor control application requires a high level of performance/efficiency then it may be necessary to increase the control loop frequency, to reduce the lag between the rotor and the rotating magnetic field generated by the FOC controller. As seen in Figure 2, an FPGA based solution can deliver much higher performance than a traditional solution, especially if resources are not an issue. This high speed control capability is also beneficial to other inverter based applications like solar panel and windmill inverters that feed electrical current back into the power grid. This is also particularly beneficial for systems that require single chip multi axis solutions; it is possible to build completely parallel control systems within the FPGA resulting in no increase in control loop time regardless of the number of axes implemented.

In a practical system however there is usually a need to deliver a realistic design that keeps costs under control, this requires sharing of resources between the axes. Fortunately this can be easily achieved in the FPGA, particularly if you are using an automated tool like Altera’s DSP Builder. DSP Builder allows you to implement the FOC algorithm in Matlab Simulink and automatically generate the accelerator module that is used in the Qsys tool. Before the logic is generated by DSP Builder you can select the required level of optimisation so the amount of FPGA resources and performance can be balanced to meet your requirements.

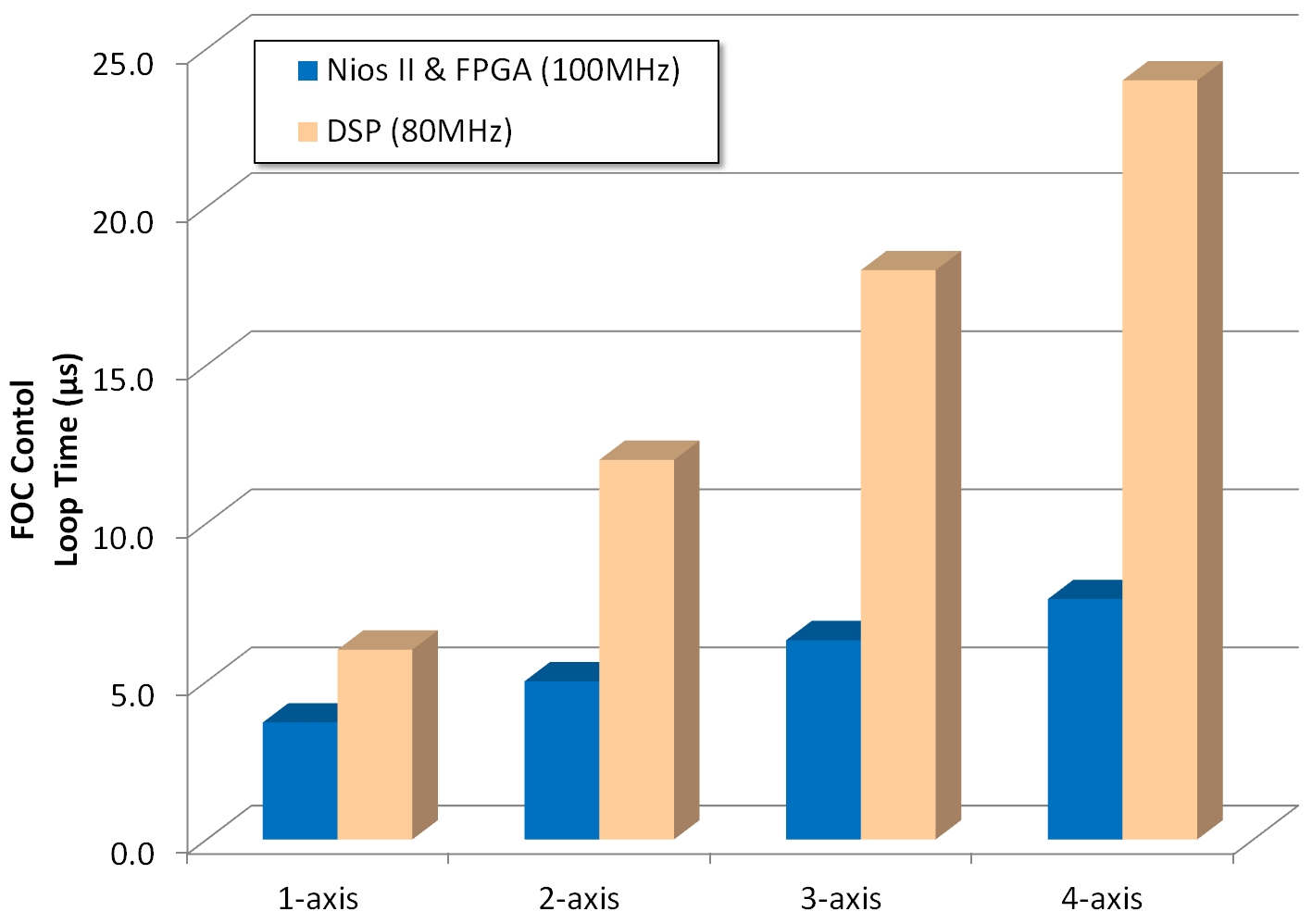

Figure 3: Comparison of optimised multi-axis solutions using FPGA and DSP

Figure 3 shows a comparison of FPGA and DSP based multi-axis control. As might be expected, the DSP delivers a simple proportional decrease in performance with the addition of extra axes – it can only process at a fixed rate so doubling the number of axes doubles the time for the control loop (as the DSP now has to calculate two loops, one per axis, for each cycle). In the FPGA, however, DSP builder is able to build pipelined logic that allows the logic to be efficiently shared between the control loops and effectively introducing zero additional processing time. As this implementation is also optimised for size there is only one Nios II processor in the system and this introduces a small additional delay for each axis as the processor has to fetch the data, launch the accelerator and process the returned output data for each axis.

The flexibility and power of the FPGA, and the recent addition of the Cortex-A9 processor, enables teams to deliver integrated system solutions that were unimaginable a few years ago.