Parallel simulator enables SoCs to get to market faster

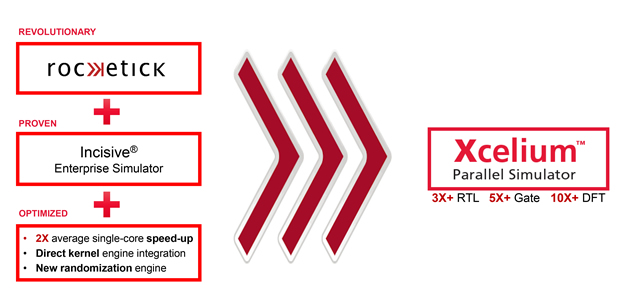

Cadence Design Systems has announced what it claims to be the industry’s first production-ready third generation simulator, the Xcelium Parallel Simulator. It is based on multi-core parallel computing technology, enabling Systems-on-Chip (SoCs) to get to market faster. On average, customers can achieve two times improved single-core performance and more than five times improved multi-core performance versus previous generation Cadence simulators.

The Cadence Xcelium simulator is production proven, having been deployed to early adopters across mobile, graphics, server, consumer, Internet of Things (IoT) and automotive projects.

“The ability for ARM and our partners to deliver products to customers’ expectations is inexorably bound to rapid and rigorous verification,” said Hobson Bullman, General Manager, Technology Services Group, ARM. “The Xcelium Parallel Simulator has demonstrated a four times speed-up for gate-level simulation and five times for RTL simulation on ARM-based SoC designs. Based on these results, we expect Xcelium can enhance our ability to deliver the most complex SoCs in a fast and highly reliable way.”

“Fast, scalable simulation is key for us to meet the tight development schedules of our complex 28nm FD-SOI SoCs and ASICs for smart driving and industrial IoT,” said Francois Oswald, CPU Team Manager, STMicroelectronics. “We measured eight times faster serial-mode DFT performance with the Cadence Xcelium Parallel Simulator, and therefore selected it as the standard simulation solution for our digital and mixed-signal SoC verification teams.”

The Xcelium simulator offers the following benefits aimed at accelerating system development:

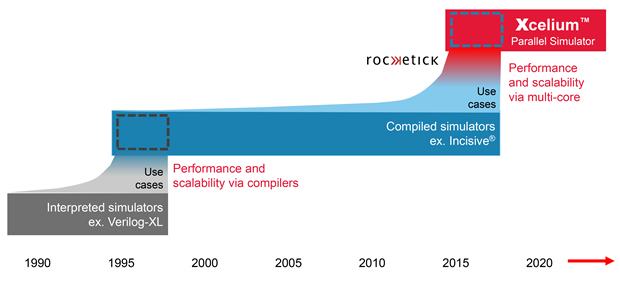

- Multi-core simulation improves runtime while also reducing project schedules: The third generation Xcelium simulator is built on the technology acquired from Rocketick and is the only fully-released simulator based on production-proven parallel simulation technology. It speeds runtime by an average of three times for Register-Transfer Level (RTL) design simulation, five times for gate-level simulation and ten times for parallel Design For Test (DFT) simulation, potentially saving weeks to months on project schedules.

- Broad applicability: The Xcelium simulator supports modern design styles and IEEE standards, enabling engineers to realise performance gains without recoding.

- Easy to use: The Xcelium simulator’s compilation and elaboration flow assigns the design and verification testbench code to the engines and automatically selects the optimal number of cores for fast execution speed.

- Incorporates several new patent-pending technologies to improve productivity: New features that speed overall SoC verification time include SystemVerilog testbench coverage for faster verification closure and parallel multi-core build.

“Verification is often the primary cost and schedule challenge associated with getting new, high-quality products to market,” said Dr. Anirudh Devgan, Senior Vice President and General Manager of the Digital & Signoff Group and the System & Verification Group, Cadence. “The Xcelium simulator combined with JasperGold Apps, the Palladium Z1 Enterprise Emulation Platform and the Protium S1 FPGA-Based Prototyping Platform offer customers the strongest verification suite on the market, enabling engineers to accelerate the pace of innovation.”

The new Xcelium simulator further extends the innovation within the Cadence Verification Suite and supports the company’s System Design Enablement (SDE) strategy, which enables system and semiconductor companies to create complete, differentiated end products more efficiently. The Verification Suite is comprised of core engines, verification fabric technologies and solutions that increase design quality and throughput, fulfilling verification requirements for a wide variety of applications and vertical segments.