IP core delivers high performance for SoC applications

A high performance, dual issue version of Cortus' APS25 IP core has been released. The APS29 is the fourth in a family of products based on the Cortus v2 instruction set. The core is aimed at embedded systems requiring good computational performance while also delivering efficient silicon area and modest power dissipation.

“For companies developing embedded systems with demanding computational requirements, our ASP29 core offers outstanding performance while efficiently using silicon area”, said Michael Chapman, President and CEO of Cortus. “It is the first of a number of Cortus cores offering greater computational performance”.

The APS29 has a Harvard architecture, 16 32-bit registers, a 64-bit accumulator and a 5-7 stage pipeline. The APS29 has two execution units, enabling it to execute up to two instructions at once, the two units are similar and both access the register set. The only difference is that one of the two ALUs features a multiply-accumulate unit, while the other has the simpler multiplier. The processor automatically dispatches the multiply-accumulate instructions to the appropriate execution unit; it also has a branch predictor and a load/store unit which will coalesce adjacent 32-bit operations into a single 64-bit operation. The core delivers 3.09 DMIPS/MHz and 3.63 CoreMarks/MHz. This is about 47% more than the comparable single issue APS25.

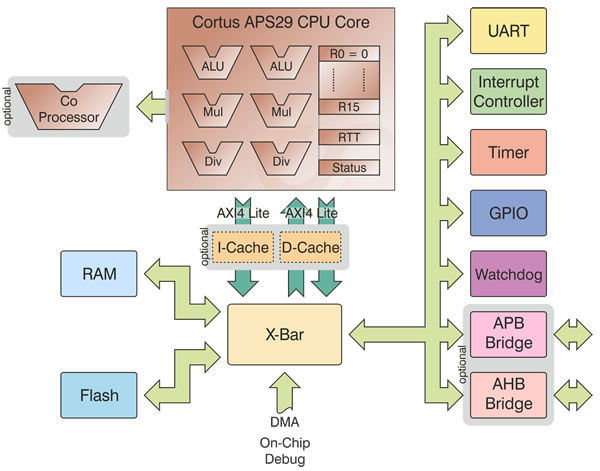

APS29 supports 64-bit AXI4 busses enabling two 32-bit reads or two 32-bit writes to be undertaken simultaneously with a 64-bit fetch for instructions. Using a 28nm technology the CPU area starts at around 0.037mm2 (optimised for area) and when optimised for speed can achieve 1,400 MHz. Up to eight co-processors can be added to an APS29 core. The Cortus coprocessor interface allows licensees to add custom coprocessors, for example to accelerate computations in cryptography or signal processing, without knowing details of the internals of the core. Co-processor instructions can be inserted into C-code appearing as function calls.

All cores interface to Cortus’ peripherals including Ethernet 10/100 MAC, USB 2.0 Device and USB 2.0 OTG. They also share the simple vectored interrupt structure which ensures rapid, real time interrupt response, with low software overhead.